Недавно AMD провела Zen 5 Tech Day, представив миру подробности о своих процессорах Ryzen 9000 «Granite Ridge» и Ryzen AI 300 «Strix Point»,

которые скоро будут выпущены. Информации было много, но на этой неделе компания продолжила с еще более глубокими подробностями о своей микроархитектуре Zen 5 и компоновке SoC. AMD сообщила, что ее «компактные» ядра Zen 5c примерно на 25% меньше стандартных полноразмерных ядер Zen 5, и что два типа ядер имеют разный объем кэша на одном кристалле — впервые для дизайна AMD. Компания также объявила о многих других интересных технических подробностях, о которых мы расскажем ниже.

SoC и Zen 5c: сокращение площади кристалла примерно на 25%

AMD разработала архитектуру Zen 5, а затем настроила ее для более компактной реализации своих ядер Zen 5c. Эта единая архитектура, развернутая в двух настраиваемых типах ядер, будет использоваться для ее настольных, мобильных и серверных процессоров и охватывать как 4-нм, так и 3-нм технологические узлы.

Подход AMD к своим «компактным» ядрам Zen 5c по своей сути отличается от подхода Intel с ее e-ядрами. Как и E-ядра Intel , ядра AMD Zen 5c разработаны так, чтобы занимать меньше места на кристалле процессора, чем «стандартные» производительные ядра, при этом обеспечивая достаточную производительность для менее требовательных задач, тем самым экономя электроэнергию и обеспечивая большую вычислительную мощность на квадратный миллиметр, чем это было возможно ранее. Но на этом сходство заканчивается. В отличие от Intel, AMD использует ту же микроархитектуру и поддерживает те же функции со своими меньшими ядрами.

Полноценные ядра AMD Zen 5 и компактные ядра Zen 5c могут использоваться в различных сегментах либо в гетерогенных конструкциях с обоими типами ядер на одном кристалле (например, Strix Point), либо в гомогенных конструкциях, в которых используется только один тип ядер (например, настольные чипы Granite Ridge только с полноразмерными ядрами или серверные чипы EPYC Bergamo предыдущего поколения только с меньшими компактными ядрами).

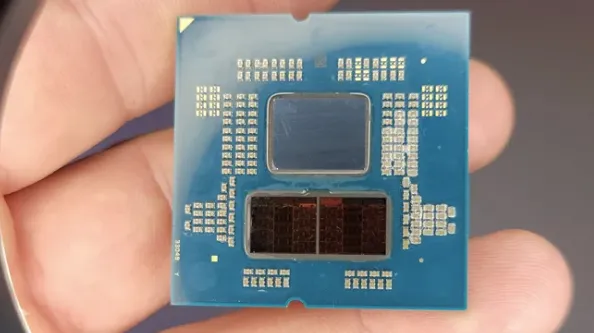

Процессоры Ryzen 9000 Granite Ridge в точности соответствуют ожиданиям — один CCD (Core Compute Die) содержит восемь полных ядер Zen 5 в паре с 32 МБ кэш-памяти L3. Процессоры будут поставляться с одним или двумя CCD в паре с IOD (Input Output Die), который обрабатывает множество других функций, присутствующих в современных SoC.Изображение 1 из 1

Strix Point SOC совершенно уникален. Компактные ядра разработаны для масштабируемой производительности, обеспечивая при этом более оптимальное соотношение мощности и производительности. Частично разница обусловлена тем, что AMD использует разные объемы кэша для этого типа ядер.

Кристалл имеет два CCX (Core Complexes — кластеры ядер на одном кристалле), как мы видели в старых чипах AMD Zen 2. Оба типа ядер имеют свои собственные кэши L1 и L2, но 24 МБ кэша L3 разделены на 8 МБ для стандартных ядер и 16 МБ для компактных ядер Zen 5c.

Ядра Zen 5c от AMD знаменуют собой первый случай, когда на одном кристалле два типа ядер имеют разные объемы кэша — четыре полноразмерных производительных ядра имеют 4 МБ L3 каждое для удовлетворения рабочих нагрузок с низкой задержкой и пиковыми нагрузками. Напротив, восемь компактных ядер имеют всего 1 МБ L3 каждое для рабочих нагрузок с низким использованием и высокой резидентностью.

Уменьшенная емкость кэша L3 не только экономит место для компактных ядер, но и радикально снижает энергопотребление — чип использует гораздо меньше энергоемкого кэша на компактное ядро. Учитывая, что AMD хотела бы запустить всю машину на компактных ядрах как можно дольше, одновременно ограничивая питанием производительные ядра и их большие кэши L3, это имеет огромный потенциал для увеличения срока службы батареи — при условии, что механизмы планирования работают так, как задумано.

Переход к асимметричной конструкции кэша представляет новые проблемы планирования и управления для AMD. Эти два кэша L3 должны взаимодействовать друг с другом через фабрику данных, во многом подобно механизму когерентности кэша CCX-CCX, обнаруженному в старой архитектуре AMD Zen 2. Это приводит к более высокой задержке для передач кэш-кэш, которая, по словам AMD, «не больше, чем вам пришлось бы обращаться к памяти».

Таким образом, AMD использует механизмы планировщика Windows, чтобы попытаться ограничить рабочие нагрузки либо ядрами Zen 5, либо 5c, чтобы уменьшить возникновение передач с высокой задержкой, при этом фоновые рабочие нагрузки обычно назначаются ядрам 5c.

В отличие от Intel, которая отдает приоритет планированию работы в своих ядрах E, прежде чем отправлять ее на другие ядра, если меньшие ядра недостаточно быстры, AMD не имеет предпочтений относительно того, куда рабочие нагрузки попадают в первую очередь. Вместо этого AMD позволяет операционной системе выбирать тип ядра для целевого использования на основе приоритета и механизмов QoS, тем самым обеспечивая наилучший возможный пользовательский опыт на основе данной рабочей нагрузки. AMD имеет свои собственные механизмы планирования потоков и предоставляет ОС таблицы, которые перечисляют характеристики производительности и мощности для каждого ядра, а также предоставляет веса для различных операций, тем самым позволяя ОС принимать решения о планировании.

Мы также можем увидеть разбивку EPYC SoC на слайде, при этом AMD скромничает по поводу своих процессоров Zen 5 EPYC следующего поколения, просто перечисляя ядра «N-Classic/Compact» на CCD, чтобы сохранить в тайне количество ядер для CCD — хотя, если традиция сохранится, это будет то же количество ядер на CCD, что и у настольных компонентов. То же самое мы видим и в списке «X-MB L3». В пункте «будущие» перечислены как однородные, так и разнородные типы чипов рядом с CCD EPYC, что некоторые могут воспринять как намек на то, что у AMD могут быть чипы Zen 5 EPYC со смешанными типами ядер — это было бы впервые. Однако обратите внимание, что список пунктов представляет собой эмпирический список характеристик, а не связан исключительно с CCD EPYC, перечисленными рядом с ним.

AMD также расширила свое обоснование и цели для компактных ядер Zen 5c. В отличие от подхода Intel, оба типа ядер Zen 5 поддерживают SMT и один и тот же набор инструкций (ISA), избегая проблем планирования, с которыми Intel сталкивается из-за своих разнородных типов ядер (типы ядер Intel не поддерживают один и тот же ISA).

Подход AMD также отличается от подхода Intel, поскольку он отдает приоритет сохранению производительности ядер Zen 5c как можно ближе к стандартным ядрам во время многоядерных рабочих нагрузок. Это предотвращает ситуации, когда более крупные ядра ждут завершения рабочих нагрузок на более мелких ядрах (важно для таких ситуаций, как многоядерные рабочие нагрузки с зависимостями потоков). Это обходит то, что Майк Кларк, ведущий архитектор Zen, называет «обрывом планирования», когда возникнет большая разница в производительности, если рабочая нагрузка запланирована на ядро Zen 5c, что негативно скажется на пользовательском опыте.

В конечном счете, цель состоит в том, чтобы обеспечить наименьшую возможную разницу между двумя типами ядер. Поэтому вместо того, чтобы установить целевой показатель дизайна Zen 5c, предсказанный определенным требованием к площади кристалла, AMD вместо этого нацелилась на определенную кривую напряжения/частоты (V/F) для меньших ядер.

Как и у всех процессоров, тактовая частота Zen 5 будет падать по мере загрузки большего количества ядер из-за ограничений по мощности и температуре. Поэтому, когда активны четыре ядра производительности, процессор будет иметь более низкую тактовую частоту, чем при одном активном ядре. AMD использовала загруженную частоту в качестве ориентира для определения целевой кривой V/F для компактных ядер, тем самым сохраняя дельту скорости между двумя типами ядер.

Снижение целевой частоты Zen 5c позволило компании разбить конструкцию на меньшее количество более крупных блоков, которые размещаются ближе друг к другу, что обеспечивает преимущества снижения энергопотребления. AMD удалила высокоскоростной повторитель и буферную схему, которые больше не были нужны в ядрах 5c для достижения максимальных частот, поддерживаемых стандартными ядрами. В сочетании с меньшей емкостью кэш-памяти L3 на ядро, площадь кристалла Zen 5c была значительно уменьшена по сравнению со стандартными ядрами.

В конечном итоге AMD уменьшила площадь для ядер Zen 5c примерно на 25% по сравнению со стандартными ядрами Zen 5 (Кларк отмечает, что это приблизительная цифра). Это меньше 35%-ного сокращения, которое мы наблюдали с ядрами Zen 4c, используемыми в процессорах EPYC Bergamo (слайд выше для справки).

Кларк сказал, что ядро Zen 5 может быть уплотнено еще больше для конструкций с компактными ядрами (однородными) с различными целевыми показателями производительности (для справки, Bergamo имеет только компактные ядра), но эта конструкция соответствует целям для этой конкретной гетерогенной конструкции. Поэтому мы можем увидеть появление еще более плотных конструкций ядер Zen 5c с другими продуктами.

Не заблуждайтесь, 25%-ное сокращение площади ядра для Zen 5c впечатляет, особенно если AMD удалось сохранить дельты производительности между ядрами низкими. Однако только тестирование покажет. Мы также не можем найти тактовые частоты для ядер Zen 5c, указанные на сайте AMD, но мы следим за более подробной информацией.

AMD Strix Point SoC

Здесь мы можем увидеть более подробную разбивку Strix Point SoC. Наиболее интересными являются различные ширины каналов данных между различными вычислительными блоками. Эти каналы данных взаимодействуют с памятью через Infinity Fabric.

Кластеры ядер Zen 5 и Zen 5c имеют собственный порт 32B/цикл, что означает, что передача данных из кэша L3 в кэш между CCX будет иметь ограничения.

Между тем, жадный до пропускной способности графический процессор имеет четыре порта 32B/цикл. Нейронный процессор XDNA (NPU) также имеет свой собственный интерфейс 32B/цикл к фабрике данных.

Мы также видим стандартный набор фиксированных функциональных ускорительных блоков, таких как видеокодирование/декодирование и т. п. Strix поддерживает память LPDDR5-7500 и DDR5-5600.

Примечательно, что AMD сократила распределение полос PCIe. Как это обычно бывает с мобильными компонентами, AMD возвращается к интерфейсу PCIe предыдущего поколения — в данном случае PCIe 4.0 — для экономии энергии. Однако AMD также сократила количество полос подключения с 20 до 16, заявив, что это решение было принято, поскольку компания определила, что дополнительные четыре полосы почти всегда используются для вторичного хранения. Однако AMD утверждает, что такой вариант использования не является распространенным в этом сегменте (низкая скорость подключения). Таким образом, AMD определила, что сокращение количества полос является приемлемым компромиссом, который привел к уменьшению количества контактов, что помогло сэкономить площадь кристалла и подложки (уменьшилось количество подключений к кристаллу и системной плате) при дальнейшем снижении энергопотребления.

AMD Granite Ridge SoC

Granite Ridge SoC в настольных чипах Ryzen 9000 имеет меньше сюрпризов — компоновка похожа на чипы предыдущего поколения. Фактически, SoC использует тот же I/O Die (IOD), что и чипы Zen 4 Ryzen 7000. Это означает ту же поддержку памяти DDR5-5600, 28 полос PCIe 5.0, пять портов USB и четыре потока отображения от графического движка RDNA 2.

Использование того же IOD следует стандартной политике AMD по интеллектуальному повторному использованию, где это возможно. Движок RDNA 2 достаточен для целей AMD — он действительно предназначен только для подсветки дисплея и ничего более. Он также позволяет AMD сохранить тот же размер корпуса, что и раньше, тем самым облегчая ее усилия по дальнейшей поддержке платформы AM5. iGPU имеет два порта 32B/цикл для Infinity Fabric.

IOD сопряжен с одним или двумя восьмиядерными комплексными кристаллами (CCD). Процессоры с одним CCD имеют порт чтения/записи 32B/цикл для связи с IOD через соединение «кристалл-кристалл» (D2D) Infinity Fabric. Однако, как и прежде, чипы с двумя CCD имеют соединение записи 16B/цикл и чтения 32B/цикл между IOD для экономии энергии на мощных SERDES, а также для упрощения компоновки корпуса (здесь важен размер интерфейса, так как конструкция более ограничена пространством с двумя кристаллами). AMD заявляет, что охарактеризовала реальные рабочие нагрузки и обнаружила типичное соотношение чтения к записи 3 к 1, поэтому производительность в значительной степени не влияет на уменьшенную пропускную способность записи 16B/цикл.

| Codename | Cores | Die Size | Transistor Count | Node | Transistor Density |

| Ryzen 7000 ‘Durango’ | 8 Zen 4 | 71 mm^2 | 6.5 billion | 5 nm | 92.9 MTr/mm^2 |

| Ryzen 9000 ‘Eldora’ | 8 Zen 5 | 70.6 mm^2 | 8.315 billion | N4P | 117.78 MTr/mm^2 |

| Hawk Point 1 | 8 Zen 4 | 178 mm^2 | ? | N4 (?) | ? MTr/mm^2 |

| Hawk Point 2 | 2 Zen 4 + 4 Zen 4c | 138 mm^2 | ? | N4 (?) | ? MTr/mm^2 |

| Strix Point | 4 Zen 5 + 8 Zen 5c | 232.5 mm^2 | ? | N4P | ? MTr/mm^2 |

ПЗС-матрица Granite Ridge «Eldora» содержит 8,315 млрд транзисторов TSMC N4P на 70,6 мм^2 кремния, что соответствует плотности транзисторов 117,78 МТр/мм^2 — на 28% больше, чем у ПЗС-матрицы Durango в Zen 4.

Strix Point имеет кристалл размером 232,5 мм^2, что намного больше кристалла размером 178 мм^2, который был у Hawk Point предыдущего поколения. Во многом это связано с тем, что оба кристалла используют один и тот же узел процесса, но у Strix больше ядер и кэша. AMD пока не поделилась количеством транзисторов для Strix, но мы следим за подробностями.

Второй брифинг AMD содержал больше информации о микроархитектуре Zen 5, чем оригинальные слайды, представленные на мероприятии Zen 5.

AMD использовала архитектуру Zen 5 как новую основу для вычислений, поэтому в ней есть несколько заметных изменений, которые будут иметь далеко идущие последствия, поскольку компания переходит на новые версии. Многие из этих функций изложены на первом слайде, который разбивает наиболее важные изменения по сравнению с Zen 4. AMD также предоставила более подробные слайды для различных компонентов ядра и обрисовала новые расширения ISA, поддерживаемые Zen 5.

Из-за ограничений по времени мы предоставим полное описание новых микроархитектурных деталей в нашем ожидаемом обзоре. Однако обратите особое внимание на второй слайд (скорости и каналы ядра Zen 5); этот слайд содержит новую информацию о связях между различными уровнями кэша. Мы также узнали, что средняя задержка неверного предсказания Zen 5 увеличилась на один цикл (для справки, задержка неверного предсказания Zen 4 варьировалась от 12 до 18 циклов, при этом 13 циклов были обычной задержкой).

Чипы Ryzen 9000 «Granite Ridge» и Ryzen AI 300 «Strix Point» на базе Zen 5 поступят в продажу 31 июля.